Тема 6. Полупроводниковые запоминающие устройства. Назначение, основные параметры, классификация запоминающих устройств.

Общие сведения

Для хранения информации в микропроцессорных системах используются запоминающие устройства на основе полупроводниковых материалов, а также магнитные и оптические внешние носители. Внутренняя память компьютера представлена в виде отдельных интегральных микросхем (ИМС) собственно памяти и элементов, включенных в состав других ИМС, не выполняющих непосредственно функцию хранения программ и данных - это и внутренняя память центрального процессора, и видеопамять, и контроллеры различных устройств.

Внутренняя или основная память может быть двух типов: оперативное запоминающее устройство (ОЗУ) или ЗУ с произвольной выборкой (ЗУПВ) и постоянное ЗУ (ПЗУ). ОЗУ, кроме того, обозначается - (RAM, Random Access Memory), а ПЗУ - (ROM, Read Only Memory).

Получила также распространение Флэш (Flash) память, имеющая особенности и ОЗУ и ПЗУ и энергонезависимая память (Nonvolatile NV).

ПЗУ и Флэш память, также энергонезависимы.

В ОЗУ коды в соответствии с решаемыми задачами постоянно изменяются и полностью пропадают при выключении питания.

В ПЗУ хранятся управляющие работой ЭВМ стандартные программы, константы, таблицы символов и другая информация, которая сохраняется и при выключении компъютера.

ОЗУ подразделяются на статическую память (SRAM), динамическую (DRAM), регистровую (RG).

ПЗУ могут быть:

- масочными - запрограммированными на заводе

- изготовителе (ROM),

- однократно-программируемыми

- пользователем ППЗУ (PROM или OTP), многократно-программируемыми

- (репрограммируемыми) пользователем РПЗУ с ультрафиолетовым стиранием (EPROM) или c электрическим стиранием (EEPROM, Flash). Широкое распространение нашли также программируемые логические матрицы и устройства (PLM, PML, PLA, PAL, PLD, FPGA и т.д.) с большим выбором логических элементов и устройств на одном кристалле.

В зависимости от типа ЗУ элементом памяти (ЭП) может быть: триггер, миниатюрный конденсатор, транзистор с "плавающим затвором", плавкая перемычка (или ее отсутствие). Упорядоченный набор ЭП образует ячейку памяти (ЯП). Количество элементов памяти в ячейке (длина слова) обычно кратно 2n (1, 4, 8, 16, 32, 64..), причем величины свыше 8-ми достигаются, обычно, группировкой микросхем с меньшим количеством ЭП.

Количество ЭП в ЯП иногда называется длиной слова.

Основными характеристиками микросхем памяти являются: информационная емкость, быстродействие и энергопотребление.

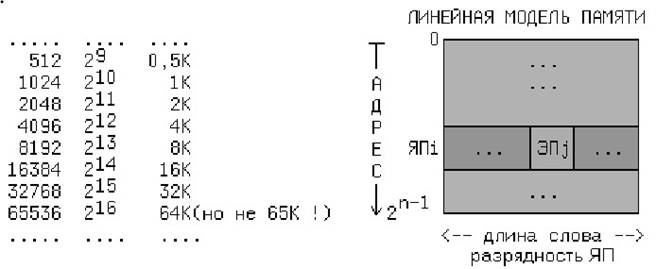

Емкость ЗУ чаще всего выражается в единицах кратных числу 210 = 1024 = 1K. Для длины слова равной биту (одному двоичному разряду) или байту (набору из восьми бит) эта единица называется килобит или килобайт и обозначается Kb или KB.

Каждой из 2n ячеек памяти однозначно соответствует "n"- разрядное двоичное число, называемое адресом ЯП. Например, адресом 511-ой ячейки будет число 1 1111 1111(BIN) = 511(DEC) = 1FF(HEX).

В программах адреса употребляются в 16-ном формате.

Рисунок 6.1 – Структура памяти

Для функционирования компьютерной системы необходимо наличие как оперативного запоминающего устройства (ОЗУ), так и постоянного запоминающего устройства (ПЗУ), обеспечивающего сохранение информации при выключении питания. ОЗУ может быть статическим и динамическим, а ПЗУ однократно или многократно программируемым.

Степень интеграции, быстродействие, электрические параметры ЗУ при записи и хранении информации, помехоустойчивость, долговременная стабильность, стабильность к внешним неблагоприятным факторам при функционировании и т.д. зависят от физических принципов работы приборов, применяемых материалов при производстве ИМС и параметров технологических процессов при их изготовлении.

Основные характеристики полупроводниковой памяти

1. Емкость памяти определяется числом бит хранимой информации.

Важной характеристикой кристалла является информационная организация кристалла памяти MxN, где M - число слов, N - разрядность слова. Например, кристалл емкостью 16 Кбит может иметь различную организацию: 16Кx1, 4Кx4 2Кx8. При одинаковом времени обращения память с большей шириной выборки обладает большей информационной емкостью.

2. Временные характеристики памяти.

Время доступа - временной интервал, определяемый от момента, когда центральный процессор выставил на шину адреса адрес требуемой ячейки памяти и послал по шине управления приказ на чтение или запись данных, до момента осуществления связи адресуемой ячейки с шиной данных.

Время восстановления - это время, необходимое для приведения памяти в исходное состояние после того, как ЦП снял с ША - адрес, с ШУ - сигнал "чтение" или "запись" и с ШД данные.

3. Удельная стоимость запоминающего устройства определяется отношением его стоимости к информационной емкости, т.е. определяется стоимостью бита хранимой информации.

4. Потребляемая энергия (или рассеиваемая мощность) приводится для двух режимов работы кристалла: режима пассивного хранения информации и активного режима, когда операции записи и считывания выполняются с номинальным быстродействием. Кристаллы динамической МОП-памяти в резервном режиме потребляют примерно в десять раз меньше энергии, чем в активном режиме. Наибольшее потребление энергии характерно для кристаллов биполярной памяти.

5. Плотность упаковки определяется площадью запоминающего элемента и зависит от числа транзисторов в схеме элемента и используемой технологии. Наибольшая плотность упаковки достигнута в кристаллах динамической МОП-памяти.

6. Допустимая температура окружающей среды обычно указывается отдельно для активной работы, для пассивного хранения информации и для нерабочего состояния с отключенным питанием.

Указывается тип корпуса, если он стандартный. Приводятся также условия эксплуатации: рабочее положение, механические воздействия, допустимая влажность и другие.

Оперативные запоминающие устройства

Полупроводниковые ЗУ подразделяются на ЗУ с произвольной выборкой и ЗУ с последовательным доступом. ЗУПВ подразделяются на:

- статические оперативные запоминающие устройства (СОЗУ);

- динамические оперативные запоминающие устройства (ДОЗУ).

ЗУ с последовательным доступом подразделяются на:

- регистры сдвига;

- приборы с зарядовой связью (ПЗС).

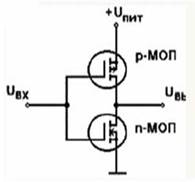

В основе большинства современных ОЗУ лежат комплиментарные МОП ИМС (КМОП), которые отличаются малой потребляемой мощностью. Это достигается применением пары МОП транзисторов с разным типом канала: n-МОП и p-МОП.

Рисунок 6.2 - Схема КМОП инвертора

ОЗУ статического типа

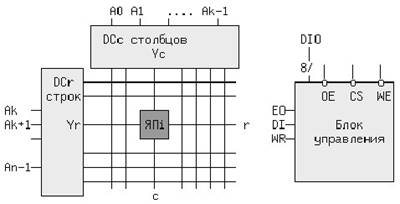

В качестве элемента памяти используется простейший D-триггер защелка. В микросхеме 537РУ10 каждая ЯП состоит из восьми триггеров и располагаются ячейки на кристалле в виде прямоугольной матрицы.

Рисунок 6.3 – Организация памяти ЯП

На рисунке приведены обозначения: nадресных входов (A0 .. An-1), DIO двунаправленная восьмиразрядная шина данных, вход разрешения выходов - ~OE, вход выбора микросхемы - ~CS и вход разрешения записи ~WE, который часто обозначают по другому ~WR/RD, подчеркивая этим, что при низком значении сигнала на этом входе производится запись байта, а при высоком уровне - чтение. EO, DI, WR - внутренние сигналы вырабатываемые блоком управления чтением/записью/хранением.

Доступ к произвольной ЯПj производится с помощью прямоугольного дешифратора, состоящего из двух обычных дешифраторов, причем k-адресных линий заводится на дешифратор столбцов (DCc), а оставшиеся n-k линий подключены к дешифратору строк (DCr). Количество строк и столбцов будет соответственно равно 2n-k и 2k, т.е. общее количество, обслуживаемых ЯП, равно

2k * 2n-k = 2n.

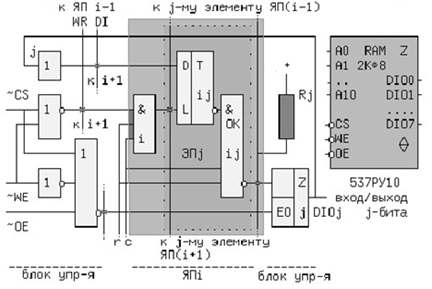

Фрагмент внутренней структуры микросхемы, по которому можно проследить основные режимы ее работы.

Рисунок 6.4 – Фрагмент внутренней структуры микросхемы

Для увеличения информационной емкости, отдельные микросхемы группируются в банки и их одноименные выходы должны объединяться. По этой причине выходы всех микросхем памяти также выполняются с открытым коллектором либо с третьим состоянием.

В ЭВМ статическое ОЗУ используется в быстродействующей Cash-памяти.

ОЗУ динамического типа

В отличие от статических ЗУ, которые хранят информацию пока включено питание, в динамических ЗУ необходима постоянная регенерация информации, однако при этом для хранения одного бита в ДОЗУ нужны всего 1-2 транзистора и накопительный конденсатор.

Рисунок 6.5 – Запоминающая ячейка динамического ОЗУ

При одинаковых размерах кристалла, информационная емкость DRAM выше, чем у SRAM.

Количество адресных входов и габариты должны увеличиться. Поэтому, адресные линии внутри микросхемы разбиваются на две группы, например старшая и младшая половина. Две одноименные k-линии каждой группы подключаются к двум выходам внутреннего k-го демультиплексора "1 в 2", а его вход соединяется с k-ым адресным входом микросхемы.

Количество адресных входов, при этом уменьшается в два раза, но зато передача адреса в микросхему должна производиться, во-первых в два приема, что несколько уменьшает быстродействие, и во-вторых потребуется дополнительный внешний мультиплексор адреса. В процессе хранения бита конденсатор разряжается. Чтобы этого не допустить заряд необходимо поддерживать.

В микросхеме динамического ОЗУ есть один или несколько тактовых генераторов и логическая схема для восстановления информационного заряда, стекающего с конденсатора.

Чаще всего и СОЗУ, и ДОЗУ выполнены в виде ЗУ с произвольной выборкой, которые имеют ряд преимуществ перед ЗУ с последовательным доступом.

Отличие динамического ОЗУ от статического:

1) мультиплексирование адресных входов,

2) необходимость регенерации хранимой информации,

3) повышенная емкость (до нескольких Мбит), 4)более сложной схемой управления.

Запоминающие устройства с произвольной выборкой

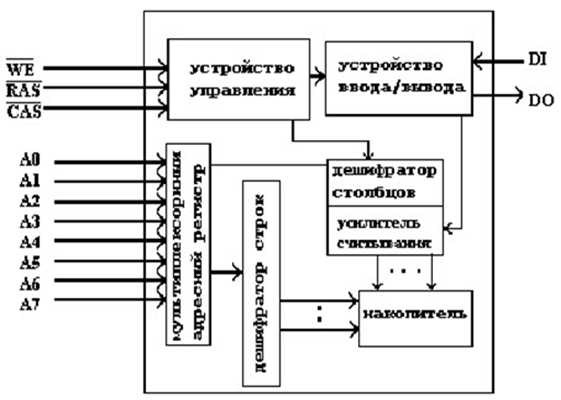

Внутренняя структура ОЗУ с произвольной выборкой 64Кx1 (КР565РУ5) (рисунок 6.6)

Рисунок 6.6

Здесь: D1-Dn (справа DI) - информационные входы; Q1 - Qn (справа DO) - инверсные выходы; A1- An - адресные входы; WE# - запись/чтение; CS# (Chip Select) - выбор кристалла; CAS# (Column Address Strobe) и RAS# (Row Address Strobe) - сигнал выборки столбца и строки соответственно.

Устройство управления включает два генератора тактовых сигналов и генератор сигналов записи и обеспечивает 4 режима работы: записи, считывания, регенерации и мультипликации адреса. Время регенерации - 2 мс.

Постоянные запоминающие устройства

Программируемые постоянные запоминающие устройства (ППЗУ) делятся на однократно программируемые (например, биполярные ПЗУ с плавкими соединениями) и рассматриваемые здесь многократно электрически программируемые МОП ПЗУ. Это полевой транзистор с плавающим затвором и МДОП (металл – диэлектрик – оксид полупроводник) транзистор. Обычно в качестве диэлектрика используют нитрид кремния.

Репрограммируемое ПЗУ

Микросхемы РПЗУ допускают многократное, до сотен тысяч, циклов перепрограммирования на рабочем месте пользователя.

Это свойство обеспечивается применением ЭП на МОП транзисторах с "плавающим затвором". Толщина изоляции "плавающего затвора" порядка 200 ангстрем. Информация считается стертой, если на выходах всех ЭП высокий уровень сигнала. В режиме программирования, на выбранный по адресной шине ЭП, куда необходимо записать ноль, подается импульс.

Стирание осуществляется УФ-излучением (EPROM), либо электрически (EEPROM). При этом все ячейки переводятся в состояние "1". Записанная информация сохраняется в течение нескольких лет. Одной из м/с этого типа является EPROM 573РФ2 с организацией (2К * 8) и тристабильными выходами.

В Flash-памяти толщина изоляции "плавающего затвора" менее 100 ангстрем, поэтому при перепрограммировании используется туннельный эффект.

Однократно программируемые ПЗУ ППЗУ (PROM,OTP)

В качестве элементов памяти имеют набор плавких перемычек, которые в процессе программирования пережигаются импульсами тока.

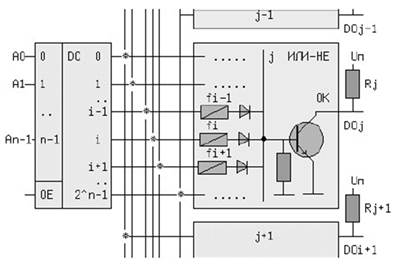

Схема ППЗУ изображена на рисунке 6.7.

Рисунок 6.7

Задания для СРС

1. Иерархическая структура памяти ЭВМ. Уровни памяти ЭВМ.

2. Важнейшие параметры ЗУ. Классификация ЗУ.

3. Основные структуры ЗУ.

4. Структура и принцип работы КЭШпамяти.

5. Элементная база ПЗУ. ROM(M), PROM, EPROM, EEPROM (E2PROM).

6. Флеш-память.

7. Элементная база статических ОЗУ.

8. Элементная база динамических ОЗУ.