Тема 4. Функциональные узлы комбинационного типа: шифраторы, дешифраторы, мультиплексоры и демультиплексоры.

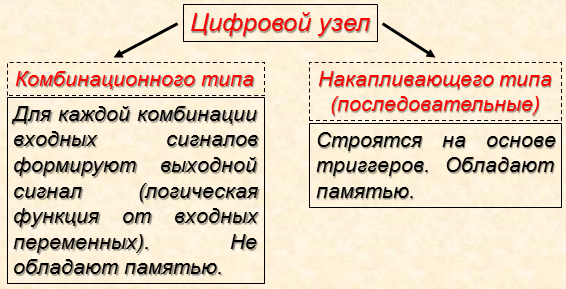

Цифровым узлом называется функциональная часть цифрового устройства, состоящая из цифровых элементов и выполняющая операции над n-разрядными двоичными кодами.

То есть цифровые узлы, у которых уровни их выходных сигналов всегда однозначно определяются текущими уровнями входных сигналов и никак не связаны с предыдущими значениями входных сигналов, называются комбинационными. Любое изменение входных сигналов обязательно изменяет состояние выходных сигналов. Именно поэтому логические элементы иногда также называют комбинационными микросхемами в отличие от последовательных (или последовательностных) микросхем, которые имеют внутреннюю память и управляются не уровнями входных сигналов, а их последовательностями.

Шифраторы

Шифратором называется комбинационный узел цифровой техники, предназначенный для преобразования входного унитарного m-разрядного кода Y(2) = ym-1ym-2…y1y0 в выходной n-разрядный двоичный код X(2) = xn-1xn-2…x1x0.

Унитарным называют код, в котором только один из т разрядов равен логической единице ("1"). Остальные т-1 разрядов равны логическому нулю ("0"). Каждому разряду унитарного кода присваивается десятичный индекс, возрастающий справа налево от 0 до т-1. Например, при т = 8 нумерация разрядов примет вид Y(2) = y7y6y5y4y3y2y1y0.

Число двоичных разрядов n, необходимых для представления унитарного кода. У(2), определяется по формуле H = log2m, с последующим округлением до большего ближайшего целого числа.

Принцип работы

Допустим, что на вход шифратора поступил 8-разрядный унитарный код y7y6y5y4y3y2y1y0 = 0 1 0 0 0 0 0 0. Под воздействием этого кода шифратор должен сформировать двоичный код, равный десятичному индексу разряда унитарного кода, равному единице. При т = 8 число разрядов двоичного кода n=3. Поскольку только у6 = 1, то на выходе шифратора должен появиться двоичный код, равный шести (110(2)).

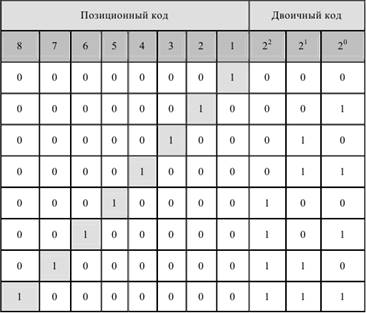

Таблица функционирования шифратора

Для наглядности, единицы располагаются по диагонали.

Для шифратора должно выполняться условие Xi∙Xj =0, i ¹ j.

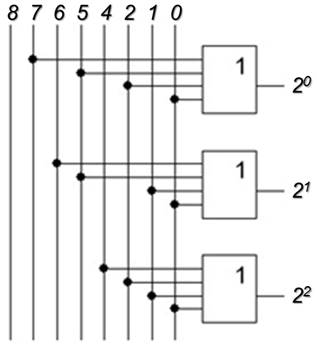

В младшем разряде (20), видно, что единице соответствуют единицы в позиционном коде, соответствующие числам 2, 4, 6, 8 (разрядам). Следовательно, эти разряды объединяются через схему «ИЛИ». Аналогичные операции проходят над старшими разрядами. В результате получим следующую электрическую схему шифратора:

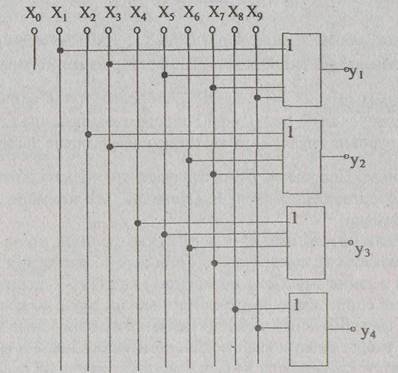

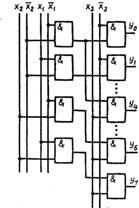

Рисунок 4.1 - Электрическая схема шифратора

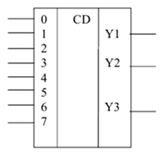

Число входов m и выходов n такого шифратора связано соотношением m = 2n. Шифратор можно использовать, например, для отображения в виде двоичного кода номера нажатой кнопки или положения многопозиционного переключателя.

Рисунок 4.2 - Условное графическое обозначение шифратора на 8 входов

Приоритетный шифратор

Шифратор, который при одновременном поступлении нескольких входных сигналов, вырабатывает выходной код только старшего разряда, имеющий наибольший вес, называются приоритетными.

Приоритетные шифраторы (priority encoder), предназначены для поиска старшей (самой левой) единицы в слове и формирования на выходе двоичного номера искомого разряда. Ещё их называют указателями старшей единицы.

Такие шифраторы применяют, например, в устройствах нормализации чисел с плавающей запятой в АЛУ микропроцессоров, в системах с приоритетным обслуживанием запросов на прерывание работы компьютера и т.д.

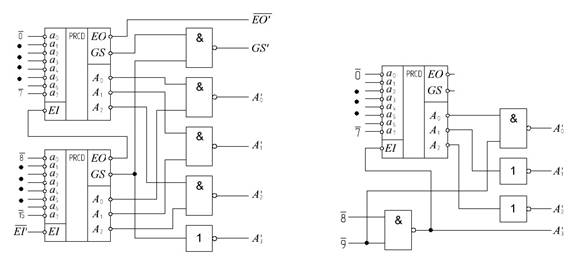

Рисунок 4.3 - Схема приоритетного шифратора

Каскадирование шифраторов

Для получения шифраторов с большим числом входов, т. е. наращивания размерности шифратора, объединяют микросхемы шифраторов с дополнительными выводами.

до шестнадцати входов. до десяти входов.

Шифратор 16→4; Шифратор 10→4.

Рисунок 4.4 – Каскадирование шифраторов

Дешифраторы

Дешифратором называется комбинационный узел, предназначенный для преобразования входного n-разрядного двоичного кода X(2)=xn-1 xn-2 … x1 х0 в выходной m-разрядный унитарный код Y = yт-1ут-2...yi…y1n y0, где n число входов, а т = 2n - число выходов.

Сущность работы дешифратора сводится к тому, что логическая "1", должна появиться на выходе дешифратора с номером, равному десятичному эквиваленту двоичного кода Х(2), например: в случае дешифратора с 3 входами и 8 выходами (n = 3 и m = 8) при x2x1x0 = 101(2) унитарный код y7y6y5y4y3y2y1y0 примет вид 00100000, т. е. только у5 = 1.

Дешифратор - функциональное цифровое устройство, предназначенное для преобразования кодов из одного вида в другой.

Дешифратор это перевод с английского слова DECODER (DC).

Классификация дешифраторов:

1. По числу разрядов.

2. В зависимости от преобразованных кодов:

- двоично-десятичный код в семисегментный;

- двоичный код в десятичное число.

3. По принципу действия:

- линейный (матричный, или одноступенчатый);

- пирамидальный (многоступенчатый).

Число входов и выходов в так называемом полном дешифраторе связано соотношением m=2n, где n — число входов, а m — число выходов.

Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

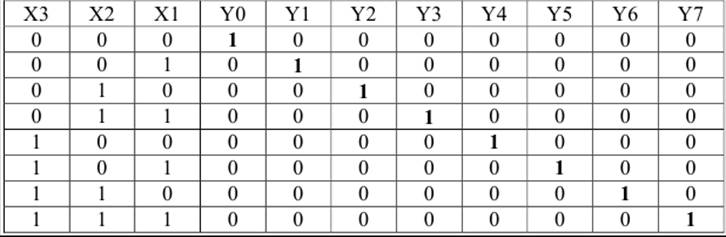

Таблица функционирования дешифратора при n=3.

Таблица 4.1

Пользуясь таблицей, составим логические функции:

Y0=![]() 3×

3×![]() 2×

2× ![]() 1; Y1=

1; Y1=![]() 3×

3×![]() 2×X1; Y2=

2×X1; Y2=![]() 3×X2×

3×X2× ![]() 1;

1;

Y3=![]() 3×X2× X1; Y4=X3×

3×X2× X1; Y4=X3×![]() 2×

2× ![]() 1; Y5=X3×

1; Y5=X3×![]() 2× X1;

2× X1;

Y6=X3×X2× ![]() 1; Y7=X3×X2× X1;

1; Y7=X3×X2× X1;

Рисунок 4.5 – Электрическая схема линейного (матричнного или одноступенчатного) дешифратора

Недостатком схемы является наличие в ней разнотипных логических элементов. Это экономически не выгодно. Данный недостаток устраняется в пирамидальных дешифраторах.

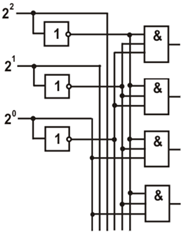

Рисунок 4.6 – Пирамидальный дешифратор

Младшие разряды двоичного числа декодируются левыми схемами «И». На входы правых схем «И» подаются сигналы с прямой и инверсной шин старшего разряда и с выходов левых схем «И». Построение пирамидального дешифратора позволяет экономить логические элементы входящие в состав схемы.

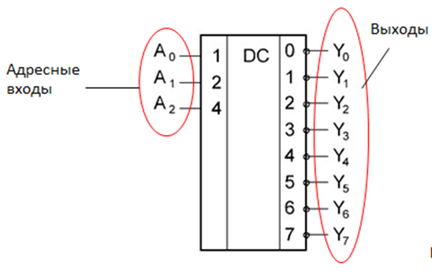

Рисунок 4.7 – Условное графическое изображение дешифратора на три входа

Расширение числа выходов дешифратора

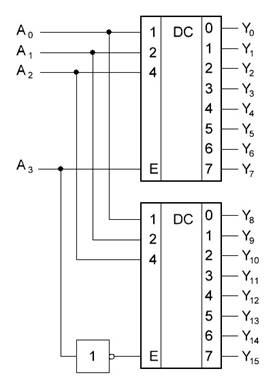

Рисунок 4.8 - Дешифратор 4→16. Параллельное соединение

Рисунок 4.9 - Дешифратор 4→10. Каскадное соединение

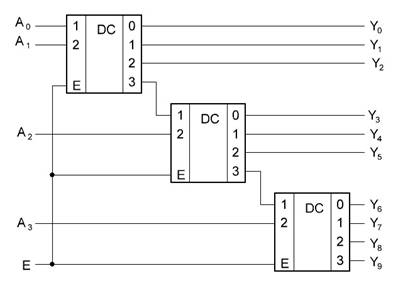

Рисунок 4.10 - Дешифратор 4→16. Пирамидальное соединение

Применение дешифраторов

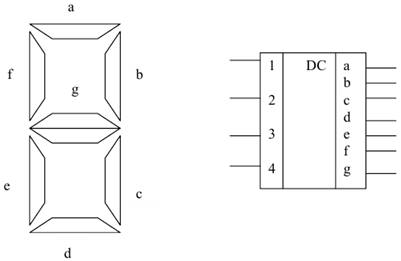

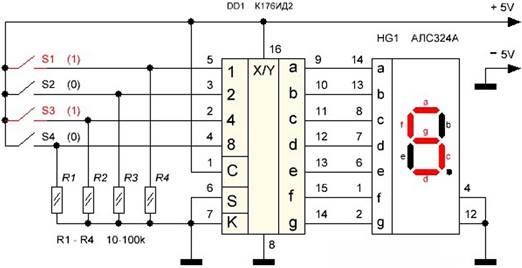

Дешифраторы с выходом на семисегментный код предназначены для отображения на цифровых индикаторах значений цифр от 0 до 9.

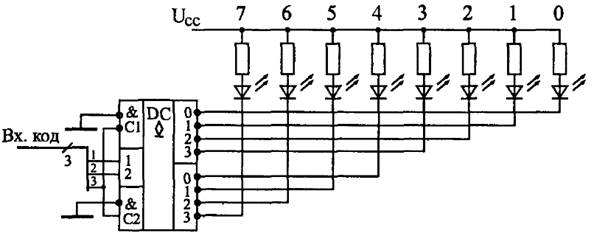

Рисунок 4.11 - Позиционная индикация на дешифраторе с выходами ОК

Рисунок 4.12 - Соединение дешифратора с 7-ми сегментным индикатором

Мультиплексоры

Мультиплексором называется функциональный узел электронного устройства, предназначенный для поочередной коммутации (переключения) информации от одного из n входов на общий выход.

Мультиплексор – это такой вид комбинационной схемы, которая осуществляет передачу сигнала с определенного входа I0… In-1 на свой единственный выход Y при условии наличия разрешающего сигнала на управляющих входах Am-1, …, A1, A0, определяющих номер подключаемого входа к выходу.

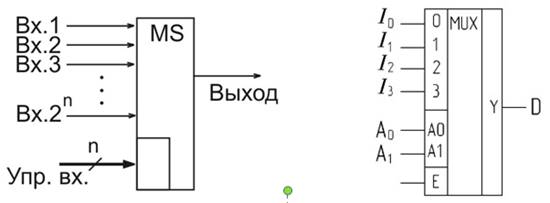

Рисунок 4.13 - Схемы мультиплексора

Номер конкретной входной линии In, подключаемой к выходу Y в каждый заданный момент (машинный такт) времени, определяется кодом, поданным на адресные входы А0, A1, ..., Аm-1.

Связь между числом информационных n и адресных m входов определяется соотношением n = 2т.

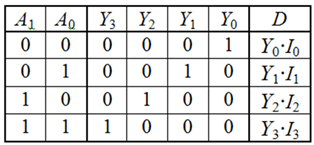

Рисунок 4.14 - Таблица истинности мультиплексора

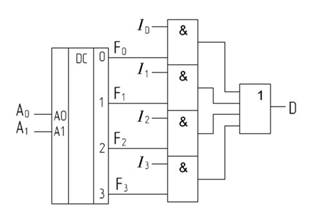

Рисунок 4.15 - Принципиальная схема мультиплексора 4→1

Мультиплексоры широко применяются в цифровой вычислительной технике. С помощью мультиплексора осуществляется временное разделение каналов связи, преобразование параллельного кода в последовательный код. Например, если на входы D0, … D7 подать параллельный код, а на адресные входы подавать двоичные коды в порядке возрастания, то получится преобразователь параллельного кода в последовательный код.

Демультиплексоры

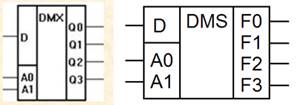

Демультиплексором называется функциональный узел компьютера, предназначенный для коммутации (переключения) сигнала с одного информационного входа D на один из n информационных выходов Y.

Номер выхода, на который в каждый такт машинного времени передается значение входного сигнала, определяется адресным кодом А0, A1, ..., Аm-1.

Адресные входы т и информационные выходы n связаны соотношением:

n = 2m или т = log2n.

Рисунок 4.16 -Демультиплексор

Демультиплексор выполняет функцию, обратную функции мультиплексора. С их помощью сигналы с одного информационного входа распределяются в требуемой последовательности по нескольким выходам.

Применительно к мультиплексорам и демультиплексорам пользуются также термином селекторы данных.

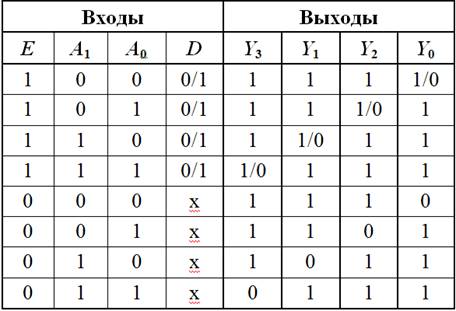

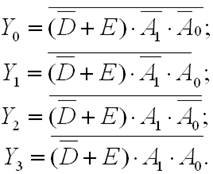

Таблица истинности демультиплексора

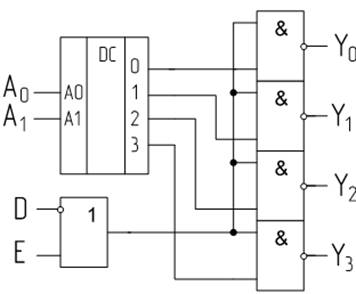

Рисунок 4.17 - Принципиальная схема демультиплексора 1→4

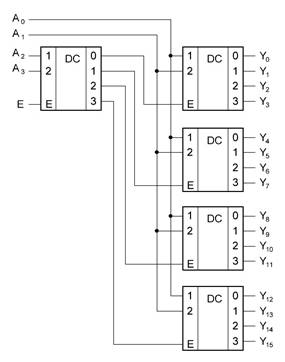

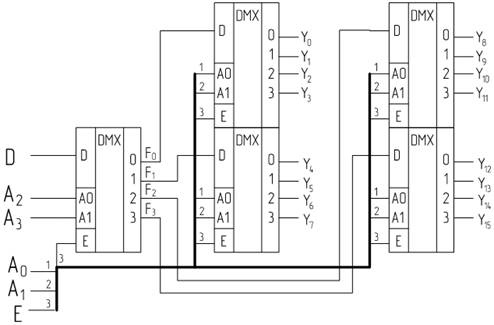

Каскадирование демультиплексоров

Если требуемое число выходных шин превышает возможности одной микросхемы, дешифраторы-демультиплексоры наращиваются в систему путём каскадирования.

Каскадирование позволяет реализовать коммутацию одного входного сигнала на произвольное число выходных линий на базе серийных микросхем меньшей разрядности.

Рисунок 4.18 - Каскадирование демультиплексоров для увеличения разрядности выходных линий

Задания для СРС

1. Определение дешифратора. Типы дешифра-торов. Внутренняя структура дешифратора.

2. Особенности дешифраторов в микро-схемном исполнении.

3. Использование дешифратора для реали-зации переключательной функции. Преимущества этого способа.

4. Двоичный шифратор, его внутренняя организация. Приоритетные шифраторы.

5. Мультиплексор. Реализация УЛМ на мультиплексоре.

6. Демультиплексор. Дешифратор с входом разрешения работы в роли демультиплексора.